Product Summary

The PEF3394HLV2.2 is a line interface Unit for DS3, STS 1 and E3. The application of the PEF3394HLV2.2 include interface for SONET/DS3 and E3 network equipment, WAN gateways, CSU/DSU, multiplexers, digital crossconnect systems, DS3/STS-1/E3 test equipment.

Parametrics

PEF3394HLV2.2 absolute maximum ratings: (1)Ambient temperature under bias, TA: -40 to 85℃; (2)Storage temperature, Tstg: -65 to 150℃; (3)IC supply voltage (digital), VDD: -0.4 to 4.5V; (4)IC supply voltage receive (analog), VDDR: -0.4 to 4.5V; (5)IC supply voltage transmit (analog), VDDX: -0.4 to 4.5V; (6)Voltage on any output pin with respect to ground, VSO: -0.4 to 4.5V; (7)Voltage on any input pin with respect to ground, VSI: -0.4 to 5.5V; (8)ESD robustness, HBM: 1.5 kΩ, 100pF, VESD,HBM: 2000V.

Features

PEF3394HLV2.2 features: (1)Generic analog interface for all DS3/STS-1/E3 applications; (2)Single chip solution for receive and transmit direction; (3)3.3 V low power device; (4)Integrated receive equalization network; (5)Integrated noise and crosstalk filter; (6)Clock and data recovery using an integrated PLL with ultra-low intrinsic jitter; (7)Transmit clock duty cycle correction PLL; (8)No external components required for clock and data recovery and receive equalizer; (9)DSX receive line monitor (additional 20 dB gain according to ANSI T1.102); (10)Low transmitter output impedances for high transmit return loss; (11)Disable function of the analog transmit line outputs; (12)Transmit pulse shaper to fulfill requirements of ANSI T1.404, Telcordia GR-499-CORE, ANSI T1.102 and ITU-T G.703 (E3); (13)Maximum line length up to 1100 ft. (using standard coaxial cable, for example AT&T 728A, 734A or 734D); (14)External line length selection (LBO) is not required; (15)Jitter specifications of GR-499-CORE and ITU-T G.823 are met; (16)Integrated jitter attenuation PLL and buffer in transmit direction; (17)Dual or single rail digital inputs and outputs from/to the framer interface; (18)Selectable line codes (HDB3 (E3), B3ZS (DS3/STS-1), AMI); (19)Analog and digital loss of signal detection and indication; (20)Automatic RDOP/RDON blanking option in case of LOS; (21)Bipolar violation indication; (22)Local loop and remote loop for diagnostic purposes; (23)Insertion of alarm indication signal (all ones); (24)Flexible hardware or software controlled device configuration; (25)Device power down function.

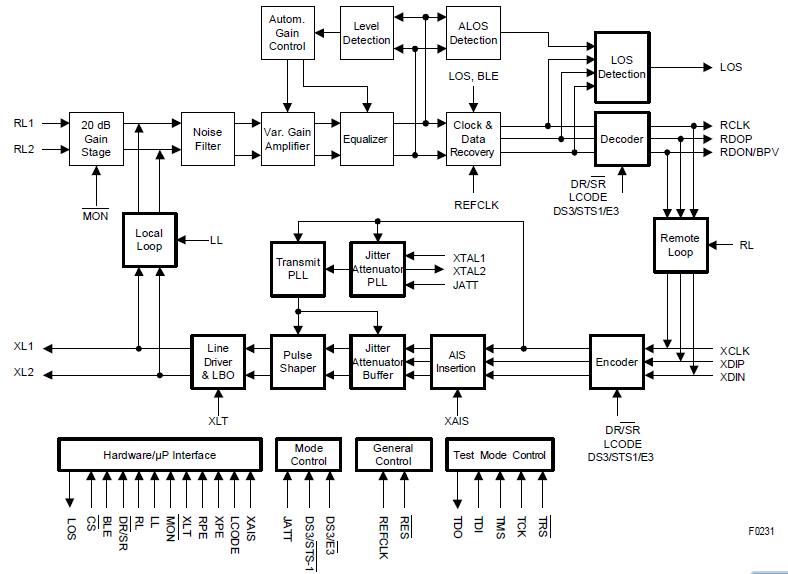

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

PEF3394HLV2.2 |

Infineon Technologies |

Audio CODECs CODEC & SLIC |

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

PEF3065 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PEF3101FV1.3 |

Infineon Technologies |

Audio CODECs VOIP CODEC'S&SLIC-DC |

Data Sheet |

Negotiable |

|

||||

|

PEF3201FV1.3 |

Infineon Technologies |

Audio CODECs VOIP CODEC'S&SLIC-DC |

Data Sheet |

Negotiable |

|

||||

|

PEF3304E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PEF3304ELV2.1-G |

Infineon Technologies |

Network Controller & Processor ICs HL V2.1. 4-channel voice codec |

Data Sheet |

Negotiable |

|

||||

|

PEF3304EV2.1-G |

Infineon Technologies |

Audio CODECs CODEC & SLIC |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))